#### C Language Constructs for Parallel Programming

**Robert Geva**

(intel) Software

Software & Services Group Developer Products Division

Copyright© 2012, Intel Corporation. All rights reserved. \*Other brands and names are the property of their respective owners. Optimization Notice 💷 5/17/13

#### **Cilk Plus**

| Parallel tasks         | <ul> <li>Easy to learn: 3 keywords</li> <li>Tasks, not threads</li> <li>Load balancing</li> </ul>  |  |

|------------------------|----------------------------------------------------------------------------------------------------|--|

| Hyper Objects          | <ul> <li>Mitigate data races on non-local<br/>variables</li> </ul>                                 |  |

| Array notations        | <ul> <li>Data-parallel array operations</li> <li>Targets SIMD</li> </ul>                           |  |

| Elemental<br>Functions | <ul> <li>Data-parallel function mapping</li> </ul>                                                 |  |

| SIMD Loops             | <ul> <li>Vectorization annotation for loops</li> <li>Single threaded vector parallelism</li> </ul> |  |

Software & Services Group Developer Products Division

Copyright© 2012, Intel Corporation. All rights reserved. \*Other brands and names are the property of their respective owners. Optimization Notice 💷 5/17/13

#### cilk\_spawn and cilk\_sync Keywords

```

int tree_walk(node *nodep)

Asynchronous recursive

{

call to tree wak

int a = 0, b = 0;

if (nodep->left)

a = _Cilk_spawn tree_walk(nodep->left);

if (nodep->right)

b = _Cilk_spawn tree_walk(nodep->right);

int c = f(nodep->value);

_Cilk_sync;

Call to f() can run in parallel

return a + b + c;

with recursive tree walks

}

Implicit sync at the end of every function keeps code well structured

Software & Services Group

Developer Products Division

Optimization

Copyright© 2012, Intel Corporation. All rights reserved.

5/17/13

3

Software

Notice 💷

*Other brands and names are the property of their respective owners

```

#### "Serialization" of Tree-walk Example

```

int tree walk(node *n)

{

int a = 0, b = 0;

if (n->left)

tree walk(n->left);

a =

if (n->right)

tree_walk(n->right);

b =

int c = f(n->value);

return a + b + c;

}

```

(Intel) Software & Services Group Developer Products Division

Copyright© 2012, Intel Corporation. All rights reserved. \*Other brands and names are the property of their respective owners. Optimization Notice 💷 5/17/13

#### **Example of keyword vs. pragma**

$X = f1(a,b) + Cilk_spawn f2(c,d);$

X =\_Cilk\_spawn f1(a,b) + f2(c,d);

- The above is currently disallow in Cilk Plus

- But this is not a necessary restriction

- Can be allowed

- The pragmas are separate from the C expression

- Hard to point out an exact point within a sub expression

Software & Services Group Developer Products Division

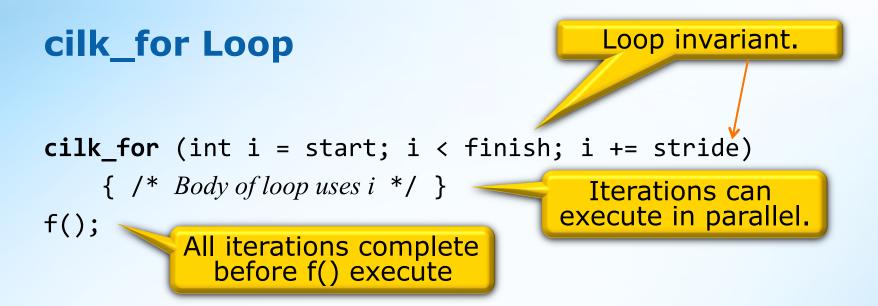

The loops has to be a countable loop Multiple linear increment allowed

Software & Services Group Developer Products Division

Copyright© 2012, Intel Corporation. All rights reserved. \*Other brands and names are the property of their respective owners.

### **Reducer Hyperobjects**

```

"Traditional" reduction on a parallel for loop:

long a[sz];

reducer_opadd<int> sum = 0;

cilk for (int i = 0; i < sz; ++i)

sum += a[i];

Parallel accesses each

get their own "view"

Generalized reduction for any code executing in parallel:

reducer opadd<int> sum = 0;

void sum_tree(node* nodep) {

if (nodep->left) cilk_spawn sum_tree(nodep->left);

if (nodep->right) cilk spawn sum tree(nodep->right);

sum += nodep->value;

}

```

Software & Services Group Developer Products Division

Copyright© 2012, Intel Corporation. All rights reserved. \*Other brands and names are the property of their respective owners

#### **Array Notation Example**

```

Serial Example

float dot_product(unsigned int sz,

float A[], float B[]) {

float dp=0.0f;

for (int i=0; i<size; i++)</pre>

dp += A[i] * B[i];

return dp;

}

Array Notation Version

float dot product(unsigned int sz,

float A[], float B[]) {

return ___sec_reduce_add(A[0:sz] * B[0:sz]);

Intrinsic reduction

Element-wise

Array

multiplication

Section

Software & Services Group

Developer Products Division

Optimization

Copyright© 2012, Intel Corporation. All rights reserved.

5/17/13

```

\*Other brands and names are the property of their respective owners

8

Notice 💷

#### **Rank and Shape**

An array section doesn't have a new kind of type

- the type of an array section is exactly that of the analogous subscript expression.

- Additionally, an array section has rank and shape.

- A section implicitly iterates over some elements of an array.

- Rank is the number of levels of loop nesting (i.e. dimensions) in the iteration space.

- Shape is a (mathematical) vector of lengths. (The rank is the same as the length of the shape vector.)

Software & Services Group Developer Products Division

#### **Rank and Shape (continued)**

The rank of an expression is determined statically. In general the shape of a section is determined dynamically.

| Expression  | Rank | Shape |

|-------------|------|-------|

| a[0]        | 0    |       |

| a[0:n]      | 1    | n     |

| a[0][i:10]  | 1    | 10    |

| a[i:n][j:m] | 2    | n×m   |

Software & Services Group Developer Products Division

Copyright© 2012, Intel Corporation. All rights reserved. \*Other brands and names are the property of their respective owners. Optimization Notice

#### Shapes have to match

- If array size is not known, both lower-bound and length must be specified

- Section ranks and lengths ("shapes") must match.

- Scalars are OK.

a[0:5] = b[0:6]; // No. Size mismatch. a[0:5][0:4] = b[0:5]; // No. Rank mismatch. a[0:5] = b[0:5][0:5]; // No. No 2D->1D a[0:4] = 5; // OK. 4 elements of A filled w/ 5. a[0:4] = b[i]; // OK. Fill with scalar b[i]. a[10][0:4] = b[1:4]; // OK. Both are 1D sections.  $b[i] = a[0:4]; // No. 1D \rightarrow 0 D$

Software & Services Group Developer Products Division

Copyright© 2012, Intel Corporation. All rights reserved. \*Other brands and names are the property of their respective owners Optimization Notice 💷

#### **Array Notations** → **Vector Operations**

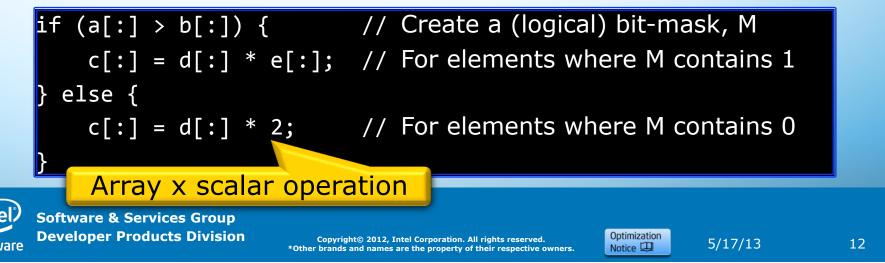

#### Selection of array elements

"vector" refers to a 1D array. Current implementation is does not allow [:] to be overloaded, e.g., for std::vector.

A[:] // All of vector A

B[2:6] // Elements 2 to 7 of vector B

C[:][5] // Column 5 of matrix C

D[0:3:2] // Elements 0,2,4 of vector D

#### Masked vector operations

#### **Vector Loop: Order of Evaluation**

```

simd_for (int n = 0; n < N; ++n) {

a[n] += b[n];

c[n] += d[n];

}</pre>

```

### **Uniform vs. Private: Illustration**

```

double b = get_position();

simd_for (int i = 0; i < N; ++i) {

double t;

t = y[i] * cos(z[i]);

a[i] = t / b;

}

```

- b is uniform, t is private

- The proposal is mapping the concepts of a uniform and a private variables onto existing syntax

- Assignments to b inside the loop shall result in uniform values, otherwise the behavior is undefined.

Software & Services Group Developer Products Division

#### **Elemental Functions - Example**

• Defining an elemental function:

```

double option_price_call_black_scholes(

double S, double K, double r,

double sigma, double time) _Simd

{

double time_sqrt = sqrt(time);

double d1 = (log(S/K)+r*time)/(sigma*time_sqrt) +

0.5*sigma*time_sqrt;

double d2 = d1-(sigma*time_sqrt);

return S*N(d1) - K*exp(-r*time)*N(d2);

}

```

Software & Services Group Developer Products Division

#### **Illustration**

```

void

vec_add ( float *r, float *op1, float *op2, int i)

simd (chunk (N))

simd (uniform (r,op1, op2) , linear (i), chunk(N))

{

r[i] = op1[i] + op2[i];

}

```

```

Two vector versions and one scalar

```

```

ssimd_for (int i = 0; i<N; ++i) {

vec_add(a,b,c,i);

}</pre>

```

```

simd_for (int i = 0; i<N; ++i) {

vec_add(a[x1[[i]],b[x2[[i]],c[x3[[i]],i);

}</pre>

```

Call matches the version with the uniforms

Call matches the version w/o the uniforms

Software

Software & Services Group Developer Products Division

Copyright© 2012, Intel Corporation. All rights reserved. \*Other brands and names are the property of their respective owners. Optimization Notice 💷

## Software

Software & Services Group Developer Products Division

Copyright© 2012, Intel Corporation. All rights reserved. \*Other brands and names are the property of their respective owners. Optimization Notice 💷 5/17/13

.3

#### **Optimization Notice**

#### **Optimization Notice**

Intel<sup>®</sup> compilers, associated libraries and associated development tools may include or utilize options that optimize for instruction sets that are available in both Intel<sup>®</sup> and non-Intel microprocessors (for example SIMD instruction sets), but do not optimize equally for non-Intel microprocessors. In addition, certain compiler options for Intel compilers, including some that are not specific to Intel micro-architecture, are reserved for Intel microprocessors. For a detailed description of Intel compiler options, including the instruction sets and specific microprocessors they implicate, please refer to the "Intel<sup>®</sup> Compiler User and Reference Guides" under "Compiler Options." Many library routines that are part of Intel<sup>®</sup> compiler products are more highly optimized for Intel microprocessors than for other microprocessors. While the compilers and libraries in Intel<sup>®</sup> compiler products offer optimizations for both Intel and Intel-compatible microprocessors, depending on the options you select, your code and other factors, you likely will get extra performance on Intel microprocessors.

Intel<sup>®</sup> compilers, associated libraries and associated development tools may or may not optimize to the same degree for non-Intel microprocessors for optimizations that are not unique to Intel microprocessors. These optimizations include Intel<sup>®</sup> Streaming SIMD Extensions 2 (Intel<sup>®</sup> SSE2), Intel<sup>®</sup> Streaming SIMD Extensions 3 (Intel<sup>®</sup> SSE3), and Supplemental Streaming SIMD Extensions 3 (Intel<sup>®</sup> SSSE3) instruction sets and other optimizations. Intel does not guarantee the availability, functionality, or effectiveness of any optimization on microprocessors not manufactured by Intel. Microprocessor-dependent optimizations in this product are intended for use with Intel microprocessors.

While Intel believes our compilers and libraries are excellent choices to assist in obtaining the best performance on Intel<sup>®</sup> and non-Intel microprocessors, Intel recommends that you evaluate other compilers and libraries to determine which best meet your requirements. We hope to win your business by striving to offer the best performance of any compiler or library; please let us know if you find we do not.

Notice revision #20101101

Software & Services Group Developer Products Division

Copyright© 2012, Intel Corporation. All rights reserved. \*Other brands and names are the property of their respective owners.

3

#### Legal Disclaimer

INFORMATION IN THIS DOCUMENT IS PROVIDED "AS IS". NO LICENSE, EXPRESS OR IMPLIED, BY ESTOPPEL OR OTHERWISE, TO ANY INTELLECTUAL PROPERTY RIGHTS IS GRANTED BY THIS DOCUMENT. INTEL ASSUMES NO LIABILITY WHATSOEVER AND INTEL DISCLAIMS ANY EXPRESS OR IMPLIED WARRANTY, RELATING TO THIS INFORMATION INCLUDING LIABILITY OR WARRANTIES RELATING TO FITNESS FOR A PARTICULAR PURPOSE, MERCHANTABILITY, OR INFRINGEMENT OF ANY PATENT, COPYRIGHT OR OTHER INTELLECTUAL PROPERTY RIGHT.

Performance tests and ratings are measured using specific computer systems and/or components and reflect the approximate performance of Intel products as measured by those tests. Any difference in system hardware or software design or configuration may affect actual performance. Buyers should consult other sources of information to evaluate the performance of systems or components they are considering purchasing. For more information on performance tests and on the performance of Intel products, reference www.intel.com/software/products.

BunnyPeople, Celeron, Celeron Inside, Centrino, Centrino Atom, Centrino Atom Inside, Centrino Inside, Centrino logo, Cilk, Core Inside, FlashFile, i960, InstantIP, Intel, the Intel logo, Intel386, Intel486, IntelDX2, IntelDX4, IntelSX2, Intel Atom, Intel Atom Inside, Intel Core, Intel Inside, Intel Inside logo, Intel. Leap ahead., Intel. Leap ahead. logo, Intel NetBurst, Intel NetMerge, Intel NetStructure, Intel SingleDriver, Intel SpeedStep, Intel StrataFlash, Intel Viiv, Intel vPro, Intel XScale, Itanium, Itanium Inside, MCS, MMX, Oplus, OverDrive, PDCharm, Pentium, Pentium Inside, skoool, Sound Mark, The Journey Inside, Viiv Inside, vPro Inside, VTune, Xeon, and Xeon Inside are trademarks of Intel Corporation in the U.S. and other countries. \*Other names and brands may be claimed as the property of others.

Copyright © 2011. Intel Corporation.

#### http://intel.com/software/products

Software & Services Group Developer Products Division

Copyright© 2012, Intel Corporation. All rights reserved. \*Other brands and names are the property of their respective owners.

# Joint proposal between Cilk Plus and OpenMP

- A minimal language

- The language does not mandate a scheduling technique

- The language allows / does not disallow dynamic load balancing

- Serial semantics and serial equivalence

- Well integrated into the C language

Software & Services Group Developer Products Division